最初呈现时间:2019年4月9日/美国东部时间下午2:00 - 3:00

主持:米歇尔罗伊

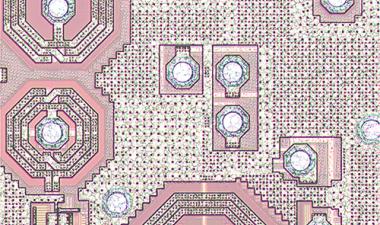

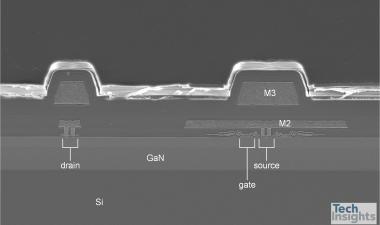

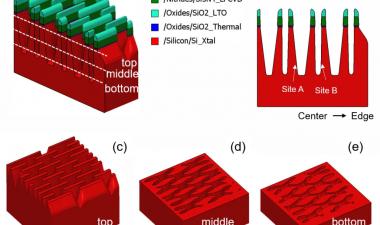

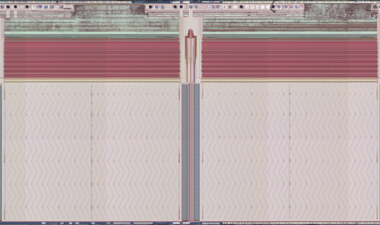

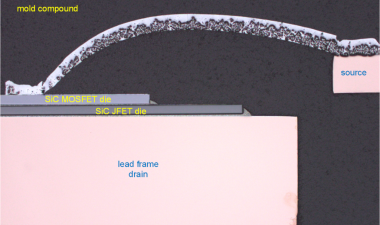

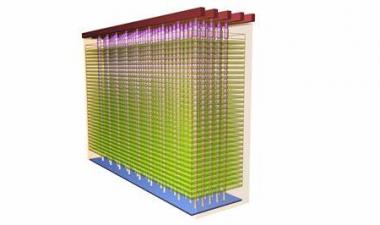

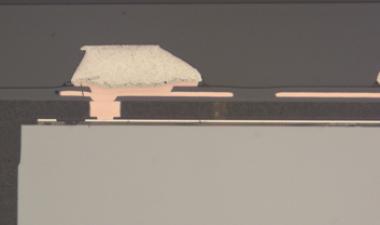

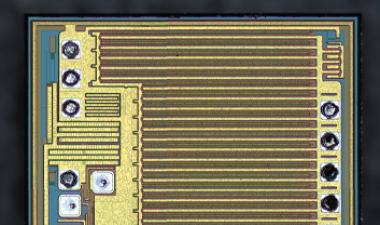

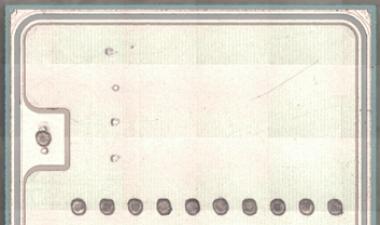

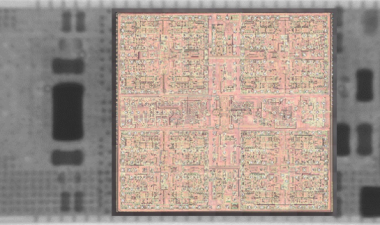

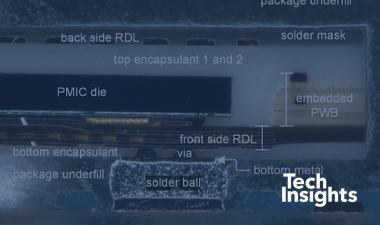

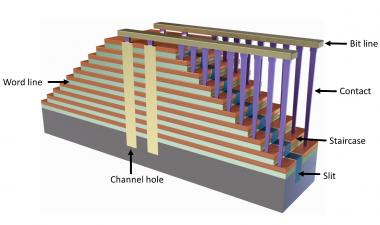

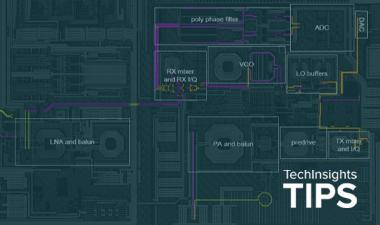

低密度扇出包技术已经存在超过十年。由于RDL计数和能力在线空间/线宽中的限制,该技术传统上已用于低至介质引脚计数应用,例如PMIC,音频编解码器和RF设备。

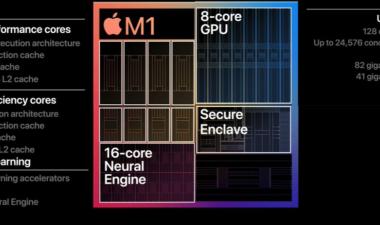

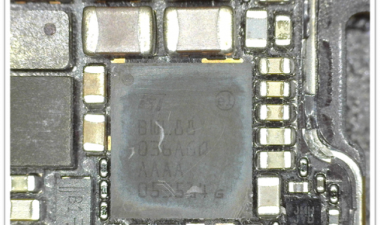

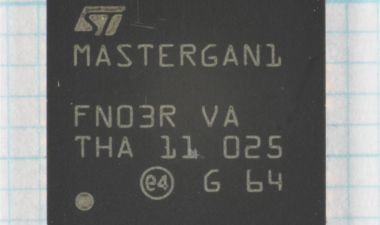

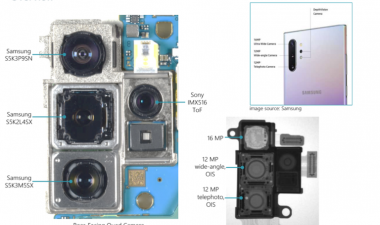

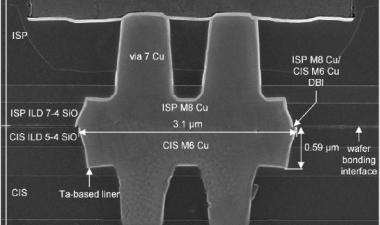

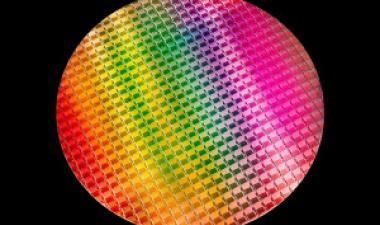

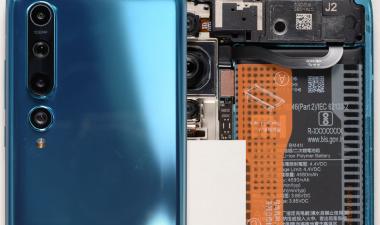

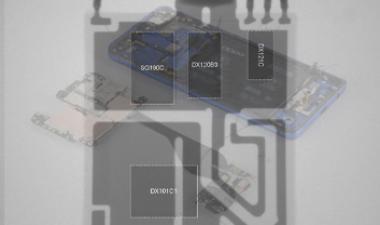

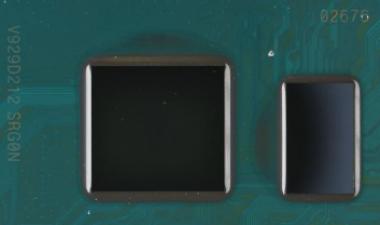

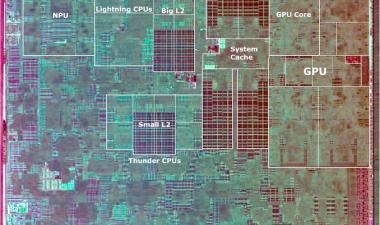

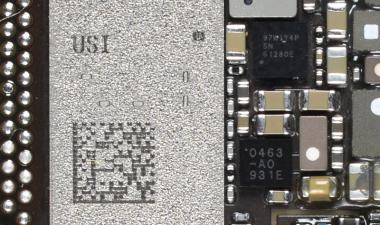

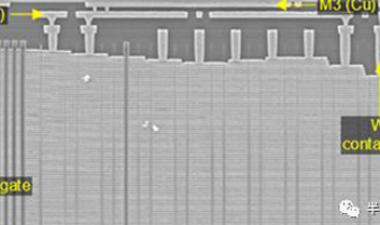

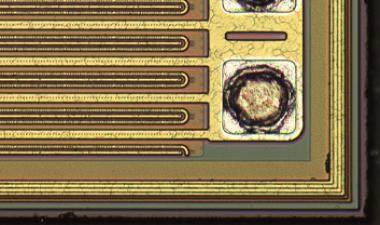

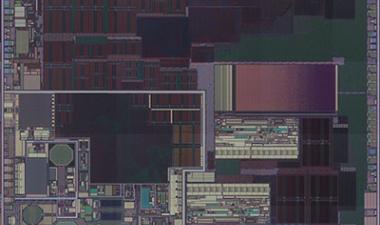

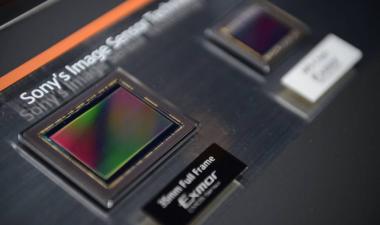

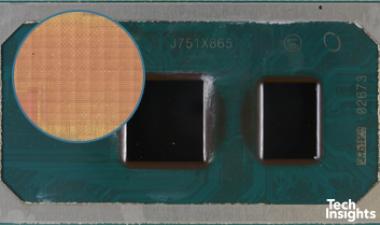

TSMC首先引入高密度晶圆的扇出封装技术解决方案,称为集成扇出(INFO)。该技术针对更高的PIN计数应用程序,例如应用处理器(AP)。Apple是这项新技术的早期采用者,首先用于iPhone 7的A10应用处理器,于2016年底推出。

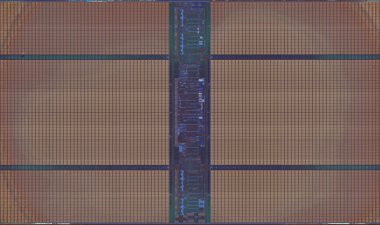

三星电子最近推出了扇形面板级封装(FOPLP)技术。FOPLP是一种高密度、基于面板的扇出封装技术,与台积电的InFO直接竞争。三星在其最新的Galaxy智能手表中首次使用FOPLP,将AP芯片和PMIC芯片封装在一起。

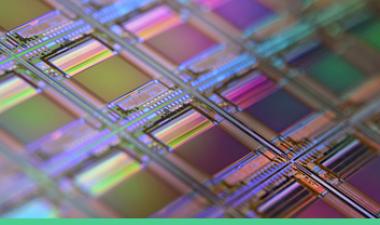

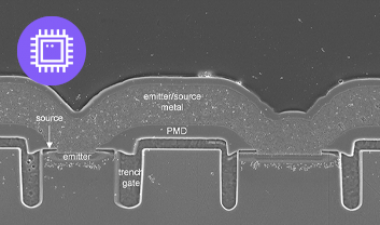

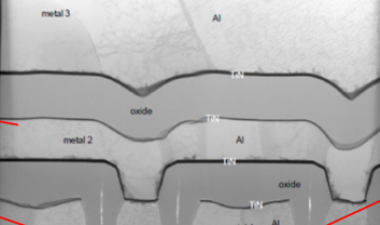

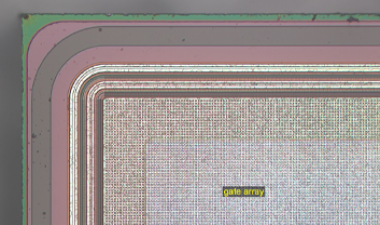

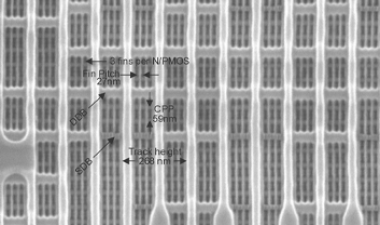

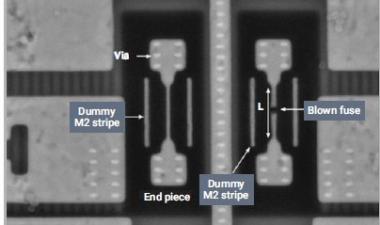

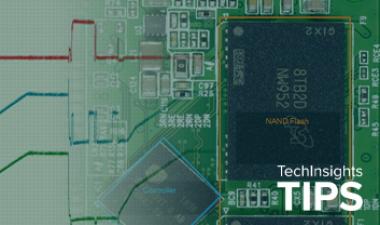

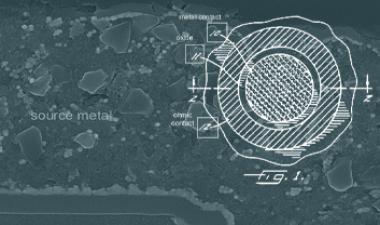

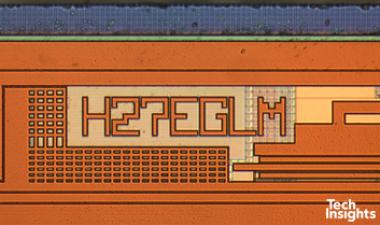

在这个网络研讨会中,我们将看看两个包装解决方案的关键结构元素。将介绍和讨论包横截面和RDL延迟图像,这将为与会者提供拟议结构的与会者,以及两种技术之间的差异。

2019年4月9日

下午2:00至3:00 ET

持续1小时

关于主人

将主持本次网络研讨会的专家

米歇尔·罗伊

高级工艺分析工程师

Michel在TechInsights担任高级过程分析工程师。他提供基于逆向工程输出的专利许可和专利评估的技术支持,以及包装的技术结构和材料分析。raybet炉石传说他在半导体封装行业拥有超过25年的专业经验,包括封装工艺工程、封装设计工程、封装可靠性和失效分析。