4部分博客系列:最先进的智能手机图像

第1部分:芯片堆叠和芯片对芯片互连

发布时间:2019年7月9日

作者:Ray Fontaine

内容改编自TechInsights在2019年国际图像传感器研讨会(IISW)上的演讲

TechInsights有幸主持了今年的IISW研讨会,并就智能手机成像技术的最新水平进行了演讲。智能手机成像代表了最高容量的成像应用程序,并在大多数情况下具有领先的成像技术元素。演讲的提纲分为四个部分:

(1)芯片堆叠和芯片对芯片互连那

(2)像素缩放和缩放支持程序那

(3)活性硅厚度和深沟槽隔离(DTI)结构,

(4)非拜耳滤色器阵列和相位检测自动对焦(PDAF)。

在这个系列的第一个博客中,将会发布芯片堆叠和tsv /Cu-Cu直接键合互连的帖子,其余的话题将在夏天发布。当然,这些只是我们的用户在我们的授权下24/7访问的深入分析的重点图像传感器订阅。

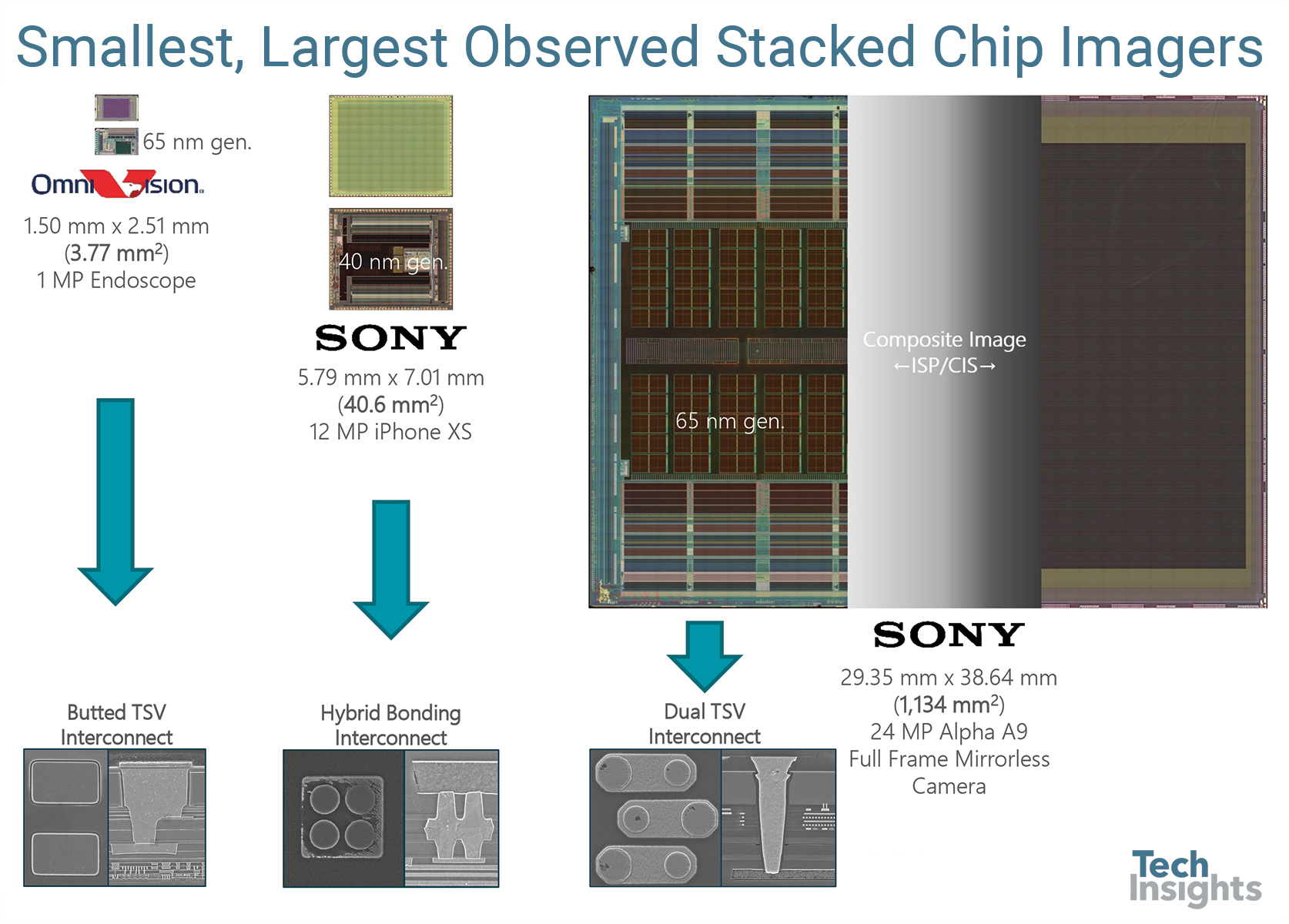

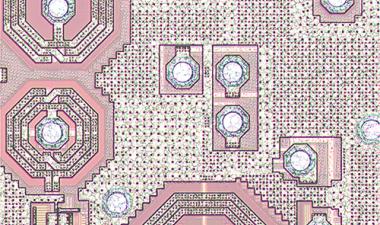

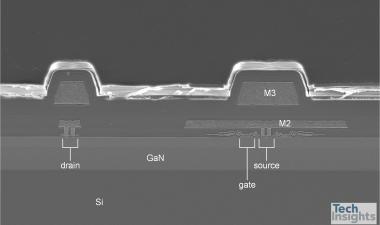

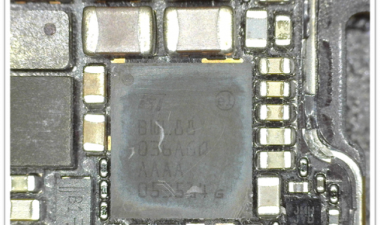

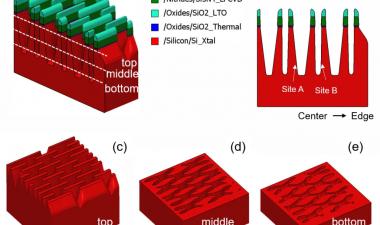

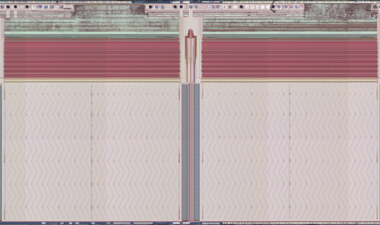

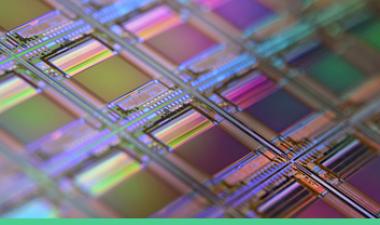

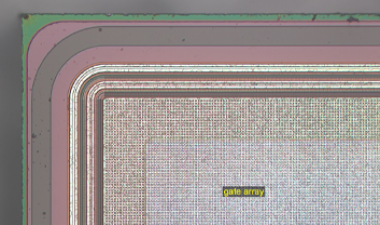

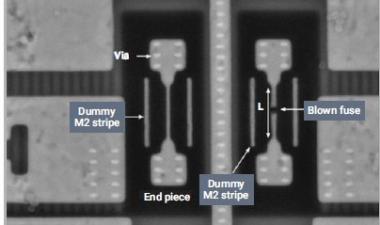

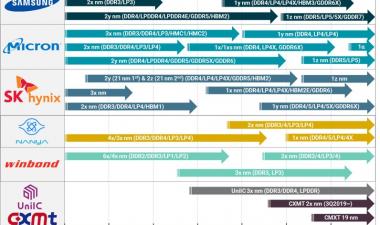

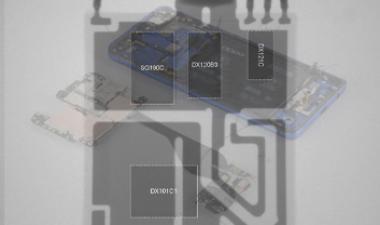

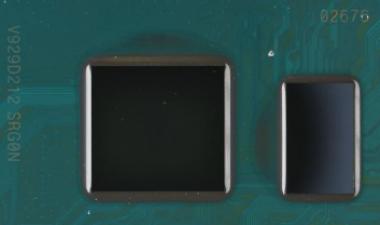

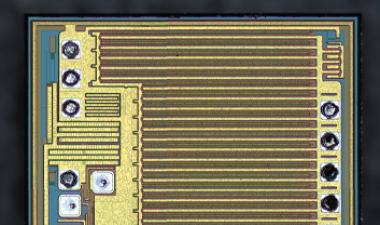

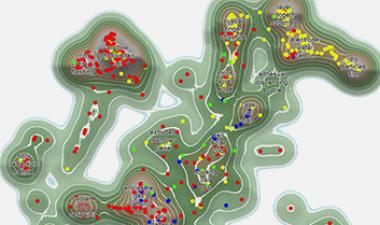

堆叠芯片成像是旗舰智能手机主摄像头的必要条件。为了进行比较,图1显示了最新的iPhone主相机双模堆叠成像仪(索尼,中间),相对于OmniVision和索尼观测到的最小和最大的双模堆叠成像仪。堆叠芯片面积和垂直互连方法之间没有相关性,但在这个系列中,我们看到了对接铜通过硅通道(TSV)、铜-铜混合键合和双TSV的使用。

图1:最小,最大的堆叠芯片成像仪

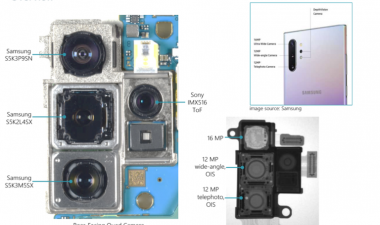

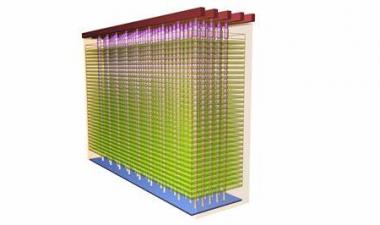

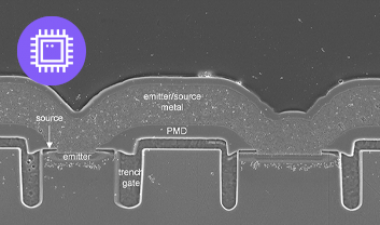

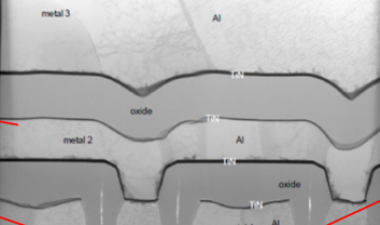

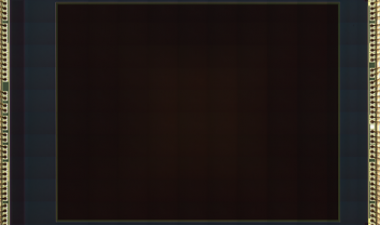

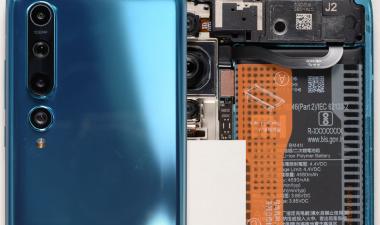

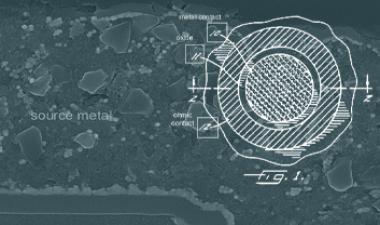

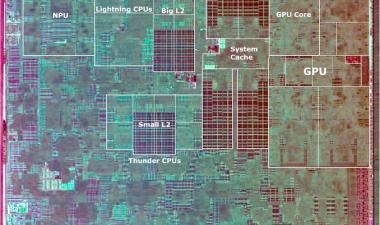

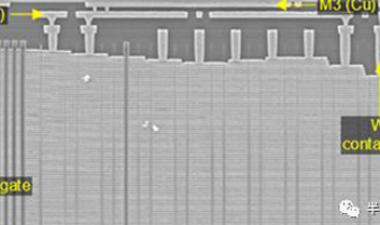

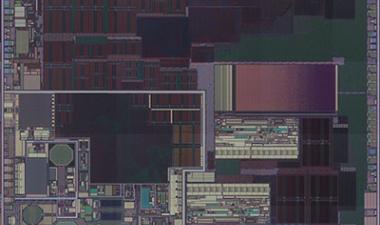

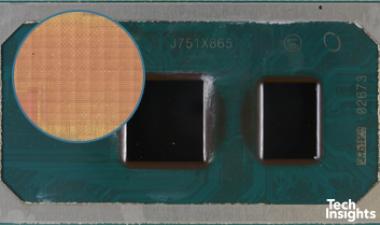

在图2中,显示了近期旗舰产品苹果、华为和三星主摄像头堆叠芯片成像仪的相对模具尺寸,并标注了有源芯片对芯片互连阵列的足迹。索尼在其使用6.0µm间距的Cu-Cu混合键合的双层叠成像仪上取得了巨大的成功。正如在IEDM 2018和其他地方展示的,小像素像素级互连正在开发中,但目前观察到的有源铜铜互连阵列仅作为TSV阵列的替代。三星电子的解决方案是在双晶片堆叠的背面安装一个DRAM晶片倒装芯片,形成一个三重堆叠的解决方案。三星更倾向于6.0µm tsv的成像到图像信号处理器(ISP)连接;进一步的细节在下一个图中详细说明。在先进的索尼堆叠成像仪中使用的ISP是在40纳米技术生成过程中制造的,而三星ISP是在28纳米技术生成过程中制造的。

图2:旗舰智能手机,主相机

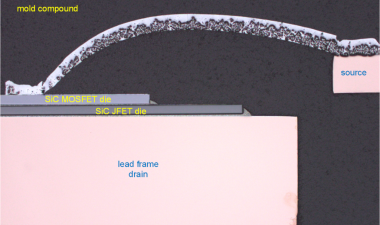

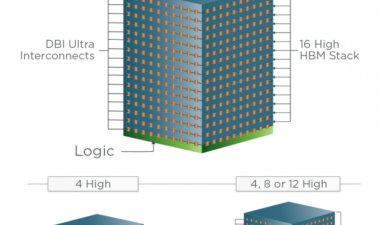

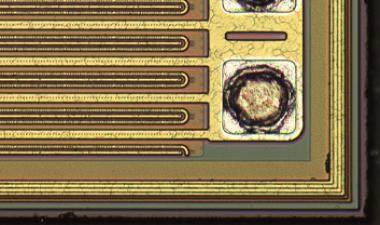

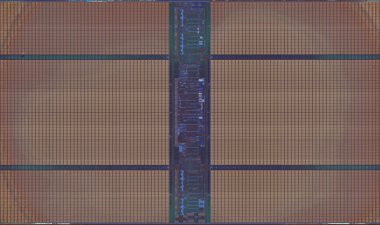

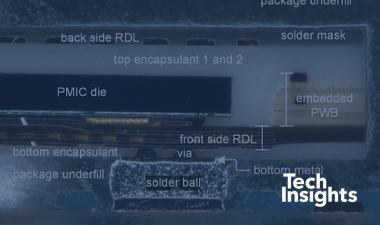

接下来的图片大多是从之前发布的内容中回收的,但作为最近索尼(Sony)和三星(Samsung)三星Galaxy智能手机的三重叠加成像结构的补充。索尼的解决方案是一个真正的三晶片堆栈,通过一个完整的TSV流互连,在一个减薄DRAM的背面包含一个再分配(RDL)层(没有注释)。三星的倒装DRAM解决方案通过ISP集成了两个RDL层和高纵横比TSV,实现了从DRAM到ISP前端的最终连接。

图3:三层堆叠的Imagers

如果您参加了研讨会,为了简洁起见,图4被略过了。它是对所选应用程序的正面照明(FI)、背面照明(BI)、堆叠式BI和三重堆叠式BI配置分布的高级评估。这一分析来自我们的报告目录,但全面的讨论超出了这篇文章的意图。相反,这是介绍图5的好方法。

图4:Imager配置热图

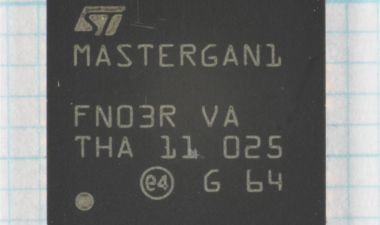

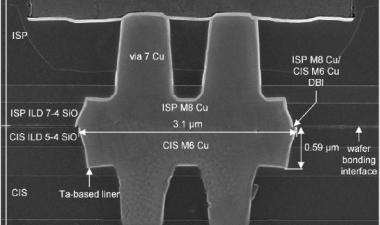

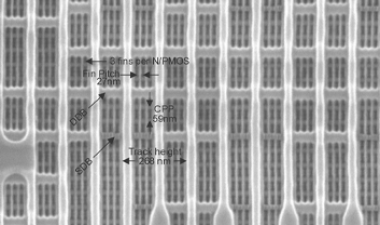

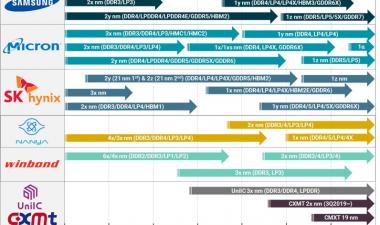

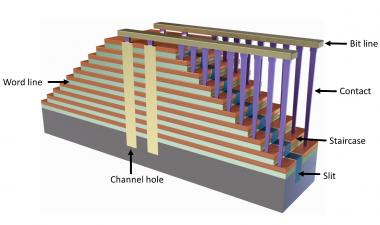

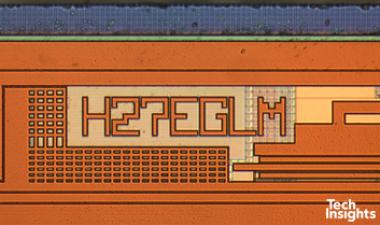

以下是三位领导人成堆的智能手机图像的简要历史。索尼推出了首个双TSV堆叠芯片,并发展为单一TSV结构。其第一代6µm间距的Cu-Cu混合键合仍在广泛使用,但我们刚刚在2019年记录了其0.8µm像素生成传感器演化到3.1µm间距的Cu-Cu混合键合。据我们所知,这是成像铜-铜混合键合沥青的世界纪录。OmniVision和铸造合作伙伴已经生产了对接TSV、单TSV和Cu-Cu直接混合粘结互连器。据我们所知,台积电保持着4.0 μ m成像单μ m的世界纪录。w填充tsv是三星堆叠成像仪的首选互连选择,我们已经在其堆叠成像仪中记录了5.0µm tsv。

图5:两个堆叠的Imagers

我们将在这里休息一下,并在夏季以一系列博客帖子的形式继续发布2019年IISW的演讲内容。下一个讨论的主题将是小像素缩放的趋势和相关技术使能器。

最先进的智能手机图像

从TechInsights在IISW 2019上的演讲中下载我们的论文和幻灯片。