发布时间:2017年6月14日

特约作者:崔正东,高级技术研究员

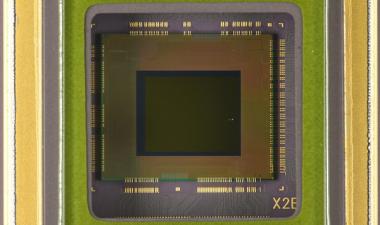

三星已经开始量产他们的第一批10纳米级DRAM产品,我们利用这个机会分析并比较了它与前几代25纳米和20纳米DRAM产品。在我们的分析中,我们发现技术节点为18纳米,我们认为这是用于设计有源图案的最小的半节距。

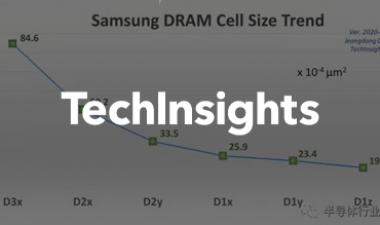

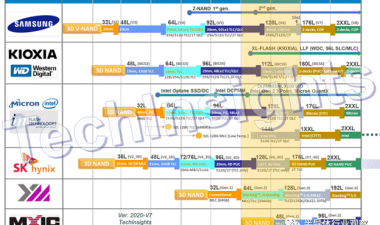

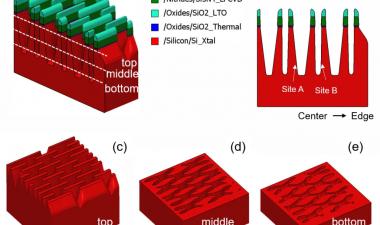

三星18nm 8gb DRAM芯片的容量为0.189 Gb/mm2.与20 nm的8 Gb硅晶片相比,存储器密度增加了32.8%,细胞大小增加了0.0026µm2)下降21.2%。图1显示了三星、SK海力士和美光的30纳米级、20纳米级和10纳米级DRAM产品的DRAM芯片尺寸和内存密度的比较。

图1所示。比较三星、SK海力士、美光的DRAM芯片尺寸和存储器密度。

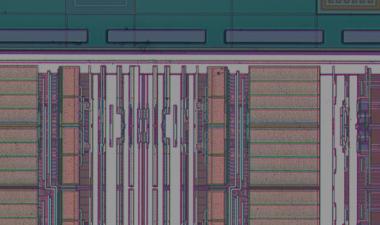

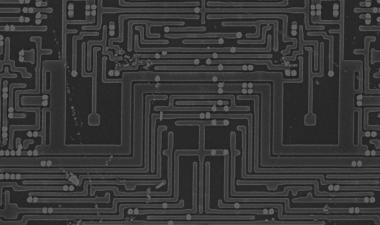

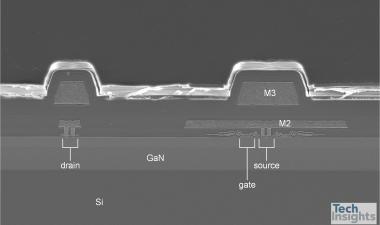

我们认为,三星18nm DRAM最具创新性的方面之一是10nm级的图形技术。三星电子在DDR4、LPDDR4、LPDDR4X等18纳米DRAM产品上首次成功开发并实现了QPT(四重图形化技术)。采用48nm的字线间距和54nm的位线间距,而有源间距为36nm,这意味着QPT对有源图案进行了集成。该技术已被用于1y nm NAND技术,特别是15 nm(东芝/SanDisk)和14 nm(三星)二维平面NAND栅(CG/FG)图形。DPT (Double Patterning Technology)用于二维平面1x和1y nm的有源位线图案。由于QPT的成熟,三星可能会加快为下一代DDR5、LPDDR5和GDDR6产品开发1y nm (15 nm) DRAM的时间。

更新!在18纳米DRAM上发现了三星的Anti-Fuse技术:使用了Kilopass 2T-cell技术

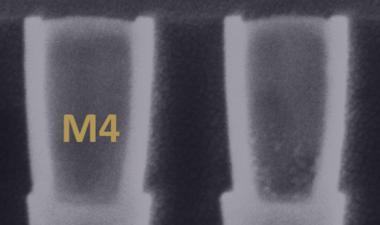

蜂窝式电容器结构采用超薄且非常均匀的ZrO/AlZrO双层高k介质。在之前的20纳米级DRAM技术中,顶部的介质层比底部更厚,使电容器看起来像倒置的锥。三星通过超精细介质沉积技术开发了一种新的材料/工艺,成功地使介质层的厚度均匀到几埃。这一技术突破使第一个10纳米级高性能和可靠性DRAM诞生。根据我们对三星18 nm DRAM电池电容结构的分析,在1.2V、300K下可以提取1.06 nm EOT(电氧化厚度)、1.77 MV/cm (ZrO)和7.4 fF/电池电容。

下载三星18nm DDR和LPDDR4X的产品信息

我们的产品信息包括:三星K3UH5H50MM-NGCJ (LPDDR4X Mobile SDRAM)和K4A8G085WC-BCRC (DDR4)